Kernel start procedure

Re: Kernel start procedure

New standard of mapper incredible required.

64 kb chunk of memory instead of 16 kb paging.

The MSX standard mapper is already similar. 256 kb for each bank, page for 64 kb.

It would give total 256 pages x 64 kb = 16 MB ! instead of 4 MB.

64 kb chunk of memory instead of 16 kb paging.

The MSX standard mapper is already similar. 256 kb for each bank, page for 64 kb.

It would give total 256 pages x 64 kb = 16 MB ! instead of 4 MB.

Re: Kernel start procedure

Paging in 64K chunks is a massive pain, definitely not something you really want to do.

Why? Because it's the entire address space. So that means the currently executing code gets paged out. And the stack. And everything related to the reason for transition needs to be held in registers.

Vast amounts of memory on 8-bit machines just really isn't worth it. There are numerous RAM expansions on the Amstrad CPC that go up to 4MB (512k was even possible back in the day) and yet, aside from a handful of demos, nothing uses them. It's too much work to create that many assets and too difficult to manage in a system that can't really juggle that much in it's limited address space.

Now if you want to prove that wrong, by all means go ahead and try coding for it. As long as you're having fun doing so, that's the main thing.

Why? Because it's the entire address space. So that means the currently executing code gets paged out. And the stack. And everything related to the reason for transition needs to be held in registers.

Vast amounts of memory on 8-bit machines just really isn't worth it. There are numerous RAM expansions on the Amstrad CPC that go up to 4MB (512k was even possible back in the day) and yet, aside from a handful of demos, nothing uses them. It's too much work to create that many assets and too difficult to manage in a system that can't really juggle that much in it's limited address space.

Now if you want to prove that wrong, by all means go ahead and try coding for it. As long as you're having fun doing so, that's the main thing.

Re: Kernel start procedure

Ah, but... scurries off and reads the SAA1099 datasheet, nope - write only, but... each disk controller has eight registers that are read / write!!! With some luck any disk left in the drive will also survive my nefarious paging schemeAndyC wrote: ↑Wed Nov 30, 2022 2:49 pm Paging in 64K chunks is a massive pain, definitely not something you really want to do.

Why? Because it's the entire address space. So that means the currently executing code gets paged out. And the stack. And everything related to the reason for transition needs to be held in registers.

Re: Kernel start procedure

One full space for cache memory could help for that just like MSX2 have it.

https://map.grauw.nl/resources/system/msxtech.pdf

>>>page 41 in browser

Processor it is not ordinary Z80 but NEC V20 [uPD-70108]. It has got Z80 emulation mode, 8086, 8088, cache memory CPU area.

8/16 architecture, 8-bit data bus, 16-bit registers

Lot of similiar machines could to have 512 kb RAM and extra cache CPU space area +64

IBM 5150

Amstrad 1512

SAM Coupe 512

Pentagon 512

Sinclair PC-200 <<<

MSX-2

ZX Spectrum with ZX512 cartridge

ZX Next even 1 MB

https://map.grauw.nl/resources/system/msxtech.pdf

>>>page 41 in browser

Processor it is not ordinary Z80 but NEC V20 [uPD-70108]. It has got Z80 emulation mode, 8086, 8088, cache memory CPU area.

8/16 architecture, 8-bit data bus, 16-bit registers

Lot of similiar machines could to have 512 kb RAM and extra cache CPU space area +64

IBM 5150

Amstrad 1512

SAM Coupe 512

Pentagon 512

Sinclair PC-200 <<<

MSX-2

ZX Spectrum with ZX512 cartridge

ZX Next even 1 MB

Last edited by TymoDEV on Thu Dec 01, 2022 2:24 am, edited 1 time in total.

Re: Kernel start procedure

OK, I have read it, Port $7FFD is useing for BANK selector according paged memory convention. 256 pages, 16 kb each one.

Total amount of RAM could give us 4 MB. System register at 0x5b5c (23388).

Total amount of RAM could give us 4 MB. System register at 0x5b5c (23388).

Re: Kernel start procedure

I am reading again ROM disassemblation, and in-fact stupid thing due lot of work to write it in ALGO.

Better oryginal ROM in procedures.

Main thing for now is ports decoding. I have already some numbers and meaning.

(c)= #31 kempston port

(c)= #23560 keyboard port

(c)= #63486 keyboard multipress port

(c)= #65533 AY sound chip ON port

(c)= #49149 AY #0 register port

(c)= #49150 AY #1 register port

(c)= #49151 AY #2 register port

(c)= #49152 AY #3 register port

(c)= #49153 AY #4 register port

(c)= #49154 AY #5 register port

(c)= #49155 AY #6 register port

(c)= #49156 AY #7 register port

(c)= #49157 AY #8 register port

(c)= #49158 AY #9 register port

(c)= #49159 AY #10 register port

(c)= #49160 AY #11register port

(c)= #49161 AY #12 register port

(c)= #49162 AY #13 register port

Better oryginal ROM in procedures.

Main thing for now is ports decoding. I have already some numbers and meaning.

(c)= #31 kempston port

(c)= #23560 keyboard port

(c)= #63486 keyboard multipress port

(c)= #65533 AY sound chip ON port

(c)= #49149 AY #0 register port

(c)= #49150 AY #1 register port

(c)= #49151 AY #2 register port

(c)= #49152 AY #3 register port

(c)= #49153 AY #4 register port

(c)= #49154 AY #5 register port

(c)= #49155 AY #6 register port

(c)= #49156 AY #7 register port

(c)= #49157 AY #8 register port

(c)= #49158 AY #9 register port

(c)= #49159 AY #10 register port

(c)= #49160 AY #11register port

(c)= #49161 AY #12 register port

(c)= #49162 AY #13 register port

Re: Kernel start procedure

It doesn't work like that. You can't access more than 128K (in very specific fixed configurations) using port $7FFD.

And the AY chip uses two ports, a register select port and a data port.

You don't need to read the ROM disassembly to find this out, there is plenty of pre-existing technical documentation on how the Speccy hardware ports work

Re: Kernel start procedure

OK, I have this from ZX NEXT,

----------------------------------------------------------------------------------------------------------------------

3.1.1 Mapped Spectrum Ports

RW Addr Mask Description

RW $103B %0001 0000 0011 1011 Sets and reads the I2C SCL line

RW $113B %0001 0001 0011 1011 Sets and reads the I2C SDA line

RW $123B %0001 0010 0011 1011 Enables layer 2 and controls paging of layer 2 screen

into lower memory (see section 3.6.8, page 81)

RW $133B %0001 0011 0011 1011 Sends byte to serial port. Read tells if data is available

in RX buffer

RW $143B %0001 0100 0011 1011 Reads data from serial port, write sets the baud rate

RW $153B %0001 0101 0011 1011 Configuration of UART interfaces

-W $1FFD %0001 ---- ---- --0- Controls ROM paging and special paging options from

the +2a/+3 (see section 3.2.7, page 41)

RW $243B %0010 0100 0011 1011 Selects active port for TBBlue/Next feature configuration (see section 3.1.3, page 34)

RW $253B %0010 0101 0011 1011 Reads and/or writes the selected TBBlue control register (see section 3.1.3, page 34)

RW $303B %0011 0000 0011 1011 Sets active sprite-attribute index and pattern-slot

index, reads sprite status (see section 3.8.7, page 100)

-W $7FFD %01-- ---- ---- --0- Selects active RAM, ROM, and displayed screen (see

section 3.2.7, page 41)

-W $BFFD %10-- ---- ---- --0- Writes to the selected register of the selected sound

chip (see section 3.10.4, page 113)

-W $DFFD %1101 1111 1111 1101 Provides additional bank select bits for extended memory (see section 3.2.7, page 41)

R- $FADF %---- ---0 --0- ---- Reads buttons on Kempston Mouse

R- $FBDF %---- -0-1 --0- ---- X coordinate of Kempston Mouse, 0-255

R- $FFDF %---- -1-1 --0- ---- Y coordinate of Kempston Mouse, 0-192

-W $FFFD %11-- ---- ---- --0- Controls stereo channels and selects active sound chip

and sound chip channel (see section 3.10.4, page 113)

RW $xx0B %---- ---- 0000 1011 Controls Z8410 DMA chip via MB02 standard (see

section 3.3.12, page 60)

R- $xx1F %---- ---- 0001 1111 Reads movement of joysticks using Kempston interface

RW $xx37 %---- ---- ---- ---- Kempston interface second joystick variant and controls joystick I/O

-W $xx57 %---- ---- 0101 0111 Uploads sprite positions, visibility, colour type and

effect flags (see section 3.8.7, page 100)

-W $xx5B %---- ---- 0101 1011 Used to upload the pattern of the selected sprite (see

section 3.8.7, page 100)

RW $xx6B %---- ---- 0110 1011 Controls zxnDMA chip (see section 3.3.12, page 60)

-W $xxDF %---- ---- --01 1111 Output to SpecDrum DAC

RW $xxFE %xxxx xxxx ---- ---0 Reading with particular high bytes returns keyboard

status (see section 3.11.3, page 118), write changes

border colour and base Spectrum audio settings (see

section 3.5.6, page 71)

RW $xxFF %---- ---- ---- ---- Controls Timex Sinclair video modes and colours in

hi-res mode. Readable when bit 2 of Peripheral 3

$08 (page 115) is set

---------------------------------------------------------------------------------------------------------------------------

from "ZX Spectrum Next Assembly Developer Guide" Tomas Kragiel

----------------------------------------------------------------------------------------------------------------------

3.1.1 Mapped Spectrum Ports

RW Addr Mask Description

RW $103B %0001 0000 0011 1011 Sets and reads the I2C SCL line

RW $113B %0001 0001 0011 1011 Sets and reads the I2C SDA line

RW $123B %0001 0010 0011 1011 Enables layer 2 and controls paging of layer 2 screen

into lower memory (see section 3.6.8, page 81)

RW $133B %0001 0011 0011 1011 Sends byte to serial port. Read tells if data is available

in RX buffer

RW $143B %0001 0100 0011 1011 Reads data from serial port, write sets the baud rate

RW $153B %0001 0101 0011 1011 Configuration of UART interfaces

-W $1FFD %0001 ---- ---- --0- Controls ROM paging and special paging options from

the +2a/+3 (see section 3.2.7, page 41)

RW $243B %0010 0100 0011 1011 Selects active port for TBBlue/Next feature configuration (see section 3.1.3, page 34)

RW $253B %0010 0101 0011 1011 Reads and/or writes the selected TBBlue control register (see section 3.1.3, page 34)

RW $303B %0011 0000 0011 1011 Sets active sprite-attribute index and pattern-slot

index, reads sprite status (see section 3.8.7, page 100)

-W $7FFD %01-- ---- ---- --0- Selects active RAM, ROM, and displayed screen (see

section 3.2.7, page 41)

-W $BFFD %10-- ---- ---- --0- Writes to the selected register of the selected sound

chip (see section 3.10.4, page 113)

-W $DFFD %1101 1111 1111 1101 Provides additional bank select bits for extended memory (see section 3.2.7, page 41)

R- $FADF %---- ---0 --0- ---- Reads buttons on Kempston Mouse

R- $FBDF %---- -0-1 --0- ---- X coordinate of Kempston Mouse, 0-255

R- $FFDF %---- -1-1 --0- ---- Y coordinate of Kempston Mouse, 0-192

-W $FFFD %11-- ---- ---- --0- Controls stereo channels and selects active sound chip

and sound chip channel (see section 3.10.4, page 113)

RW $xx0B %---- ---- 0000 1011 Controls Z8410 DMA chip via MB02 standard (see

section 3.3.12, page 60)

R- $xx1F %---- ---- 0001 1111 Reads movement of joysticks using Kempston interface

RW $xx37 %---- ---- ---- ---- Kempston interface second joystick variant and controls joystick I/O

-W $xx57 %---- ---- 0101 0111 Uploads sprite positions, visibility, colour type and

effect flags (see section 3.8.7, page 100)

-W $xx5B %---- ---- 0101 1011 Used to upload the pattern of the selected sprite (see

section 3.8.7, page 100)

RW $xx6B %---- ---- 0110 1011 Controls zxnDMA chip (see section 3.3.12, page 60)

-W $xxDF %---- ---- --01 1111 Output to SpecDrum DAC

RW $xxFE %xxxx xxxx ---- ---0 Reading with particular high bytes returns keyboard

status (see section 3.11.3, page 118), write changes

border colour and base Spectrum audio settings (see

section 3.5.6, page 71)

RW $xxFF %---- ---- ---- ---- Controls Timex Sinclair video modes and colours in

hi-res mode. Readable when bit 2 of Peripheral 3

$08 (page 115) is set

---------------------------------------------------------------------------------------------------------------------------

from "ZX Spectrum Next Assembly Developer Guide" Tomas Kragiel

Last edited by TymoDEV on Thu Dec 01, 2022 9:35 am, edited 1 time in total.

Re: Kernel start procedure

Could You send something like C includes with exact assembly procedures to service some functions?

For example I have procedure to handle sound like this:

; Write the contents of our AY buffer to the AY registers.

w8912:

ld hl,snddat ; start of AY-3-8912 register data.

ld e,0 ; start with register 0.

ld d,14 ; 14 to write.

ld c,25 ; low byte of port to write.

w8912a:

ld b,255 ; 255*256+253 = port 65533 = select soundchip register.

out (c),e ; tell chip which register we're writing.

ld a,(hl) ; value to write.

ld b,191 ; 191*256+253 = port 49149 = write value to register.

out (c),a ; this is what we're putting there.

inc e ; next sound chip register.

inc hl ; next byte to write.

dec d ; decrement loop counter.

jp nz,w8912a ; repeat until done.

ret

snddat

defw 0 ; tone registers, channel A.

defw 0 ; channel B tone registers.

defw 0 ; as above, channel C.

sndwnp

defb 0 ; white noise period.

sndmix

defb 60 ; tone/noise mixer control.

sndv1

defb 0 ; channel A amplitude/envelope generator.

sndv2

defb 0 ; channel B amplitude/envelope.

sndv3

defb 0 ; channel C amplitude/envelope.

sndenv

defw 600 ; duration of each note.

defb 0

from "How To Write Spectrum Games" rev 1.1 J.Cauldwell

Sound chip: $BFFD port (49149) and $FFFD port (65533)

For example I have procedure to handle sound like this:

; Write the contents of our AY buffer to the AY registers.

w8912:

ld hl,snddat ; start of AY-3-8912 register data.

ld e,0 ; start with register 0.

ld d,14 ; 14 to write.

ld c,25 ; low byte of port to write.

w8912a:

ld b,255 ; 255*256+253 = port 65533 = select soundchip register.

out (c),e ; tell chip which register we're writing.

ld a,(hl) ; value to write.

ld b,191 ; 191*256+253 = port 49149 = write value to register.

out (c),a ; this is what we're putting there.

inc e ; next sound chip register.

inc hl ; next byte to write.

dec d ; decrement loop counter.

jp nz,w8912a ; repeat until done.

ret

snddat

defw 0 ; tone registers, channel A.

defw 0 ; channel B tone registers.

defw 0 ; as above, channel C.

sndwnp

defb 0 ; white noise period.

sndmix

defb 60 ; tone/noise mixer control.

sndv1

defb 0 ; channel A amplitude/envelope generator.

sndv2

defb 0 ; channel B amplitude/envelope.

sndv3

defb 0 ; channel C amplitude/envelope.

sndenv

defw 600 ; duration of each note.

defb 0

from "How To Write Spectrum Games" rev 1.1 J.Cauldwell

Sound chip: $BFFD port (49149) and $FFFD port (65533)

Re: Kernel start procedure

In fact, that was error on ports, Sorry.TymoDEV wrote: ↑Thu Dec 01, 2022 6:42 am (c)= #49149 AY #0 register port

(c)= #49150 AY #1 register port

(c)= #49151 AY #2 register port

(c)= #49152 AY #3 register port

(c)= #49153 AY #4 register port

(c)= #49154 AY #5 register port

(c)= #49155 AY #6 register port

(c)= #49156 AY #7 register port

(c)= #49157 AY #8 register port

(c)= #49158 AY #9 register port

(c)= #49159 AY #10 register port

(c)= #49160 AY #11register port

(c)= #49161 AY #12 register port

(c)= #49162 AY #13 register port

Re: Kernel start procedure

I have already ports and registers:

Sound Chip: ,OK.

Joystick Sinclair 1: ,OK.

Joystick Sinclair 2: ,OK.

Joystick Kempston: ,OK.

Keyboard: ,OK.

Bank Selector: ,OK.

Interrupts: ,OK.

Vblank Synchro/timeing: ,OK.

Lots of ports: ,OK.

======================================

I am not sure if that's all ports.

Now it's time to consider Video.

I have lot of docs: for SAM Coupe, ZX NEXT, MSX2 YAMAHA YM9958,PC CGA

In SAM docs I have found this:

Ports list for Video:

$FF (255) Video TIMEX control, ATTRIBUTES register READ/WRITE

$FC (252) VMPR - Video Memory Page Register /WRITE

$FB (251) HMPR - High Memory Page Register /WRITE

$FA (250) LMPR - Low Memory Page Register /WRITE

$F9(249) LINE INTerrupt register /WRITE

$F8 (248) CLUT - Colour Look Up Table (base port) /WRITE

- MODE 1 -

32 cells x 24 lines in 2 colours from 16 out of a palette of 128

colours, giving 768 character cells (8 x 8) using 6 kilobytes of bitmapped memory and 0.75 kilo-bytes of attribute memory. This mode

emulates Spectrum memory mapping.

- MODE 2 -

32 cells x 192 lines in 2 colours from 16 out of a palette of 128

colours, giving 6144 character cells (8 x 1) using 6 kilobytes of bitmapped memory and 6 kilobytes of attribute memory. This mode has

contiguous memory addressing in two blocks.

- MODE 3 -

512 pixels x 192 lines in 4 colours out of a palette of 128 colours,

giving 98304 dots using 24 kilo-bytes of memory. This mode, when used

with a character set 6 pixels wide, will give 85 characters per line.

- MODE 4 -

256 pixels x 192 lines in 16 colours out of a palette of 128 colours,

giving 49252 dots using 24 kilo-bytes of memory. This mode is ideal for

graphic display, and when used in conjunction with LINE INTerrupt

register can display the full 128 colours on screen.

SAM Coupe can handle ZX Spectrum graphic with Mode-1

ZX Spectrum itself could drive lot of graphic modes:

>>>EN Academic Wikipedia

And at last! I have includes from z88dk package. Lot of includes for Spectrum and SAM Coupe.

Sound Chip: ,OK.

Joystick Sinclair 1: ,OK.

Joystick Sinclair 2: ,OK.

Joystick Kempston: ,OK.

Keyboard: ,OK.

Bank Selector: ,OK.

Interrupts: ,OK.

Vblank Synchro/timeing: ,OK.

Lots of ports: ,OK.

======================================

I am not sure if that's all ports.

Now it's time to consider Video.

I have lot of docs: for SAM Coupe, ZX NEXT, MSX2 YAMAHA YM9958,PC CGA

In SAM docs I have found this:

Ports list for Video:

$FF (255) Video TIMEX control, ATTRIBUTES register READ/WRITE

$FC (252) VMPR - Video Memory Page Register /WRITE

$FB (251) HMPR - High Memory Page Register /WRITE

$FA (250) LMPR - Low Memory Page Register /WRITE

$F9(249) LINE INTerrupt register /WRITE

$F8 (248) CLUT - Colour Look Up Table (base port) /WRITE

- MODE 1 -

32 cells x 24 lines in 2 colours from 16 out of a palette of 128

colours, giving 768 character cells (8 x 8) using 6 kilobytes of bitmapped memory and 0.75 kilo-bytes of attribute memory. This mode

emulates Spectrum memory mapping.

- MODE 2 -

32 cells x 192 lines in 2 colours from 16 out of a palette of 128

colours, giving 6144 character cells (8 x 1) using 6 kilobytes of bitmapped memory and 6 kilobytes of attribute memory. This mode has

contiguous memory addressing in two blocks.

- MODE 3 -

512 pixels x 192 lines in 4 colours out of a palette of 128 colours,

giving 98304 dots using 24 kilo-bytes of memory. This mode, when used

with a character set 6 pixels wide, will give 85 characters per line.

- MODE 4 -

256 pixels x 192 lines in 16 colours out of a palette of 128 colours,

giving 49252 dots using 24 kilo-bytes of memory. This mode is ideal for

graphic display, and when used in conjunction with LINE INTerrupt

register can display the full 128 colours on screen.

SAM Coupe can handle ZX Spectrum graphic with Mode-1

ZX Spectrum itself could drive lot of graphic modes:

>>>EN Academic Wikipedia

And at last! I have includes from z88dk package. Lot of includes for Spectrum and SAM Coupe.

Re: Kernel start procedure

Not really, there is a single screen mode. All those "other modes" on that list are either hardware changes in clone machines (like the Timex) or just the result of updating the screen at a high enough frequency - it's very much a stretch to describe it as a different graphics mode.TymoDEV wrote: ↑Fri Dec 02, 2022 4:08 am ZX Spectrum itself could drive lot of graphic modes:

>>>EN Academic Wikipedia

Re: Kernel start procedure

To be exact - it depends on what IM mode active. In case of "standard", it does execute ROM routines for incrementing frames counter, reading keyboard...

And again, for the 128K Speccy we can say there is some kind of two different ways to access screen.

Additionally, there are woodoo magic with multicolour or gigascreens

Re: Kernel start procedure

Two screens, but the same mode. Where mode is typically defined as some combination of pixel density and colour resolution and usually something that the hardware supports without CPU intervention.

Personally I blame C64 coders who kept describing similar hardware bashing on their machine as if it were a different display mode and, as such, muddied the water somewhat.

- 1024MAK

- Bugaboo

- Posts: 3123

- Joined: Wed Nov 15, 2017 2:52 pm

- Location: Sunny Somerset in the U.K. in Europe

Re: Kernel start procedure

I agree, all Sinclair ZX Spectrum computers (16K/48K/+/128K/+2/+2A/+2B/+3/+3B) only have one video mode.

By that, I mean that only one video display system exists which is comprised of a 256 x 192 pixels (32 x 24 characters) with 8 colours plus bright (giving 15 ‘shades’) attributes on a 32 x 24 matrix, which is fully supported by the video hardware and the firmware (ROM code).

Yes, the 128K machines (128K/+2/+2A/+2B/+3/+3B) do have two different memory areas where the screen data can be stored and displayed from. This is just part of the RAM bank switching system.

If a 48K, +, 128K or +2 (grey) is hacked with hardware modifications, more screens can be provided. But no one would describe these extra areas of memory in which the screen data can be stored and displayed from as additional video modes.

Also, the video system will continue to display the currently selected screen data regardless of what the Z80A microprocessor is doing. That includes if the Z80A is halted or it’s clock stopped.

All other video improvements that implemented by software are not normally described as video modes, because they require a lot of microprocessor time.

Although, the authors, creators, and software companies may market or describe them as a new ‘mode’.

Mark

By that, I mean that only one video display system exists which is comprised of a 256 x 192 pixels (32 x 24 characters) with 8 colours plus bright (giving 15 ‘shades’) attributes on a 32 x 24 matrix, which is fully supported by the video hardware and the firmware (ROM code).

Yes, the 128K machines (128K/+2/+2A/+2B/+3/+3B) do have two different memory areas where the screen data can be stored and displayed from. This is just part of the RAM bank switching system.

If a 48K, +, 128K or +2 (grey) is hacked with hardware modifications, more screens can be provided. But no one would describe these extra areas of memory in which the screen data can be stored and displayed from as additional video modes.

Also, the video system will continue to display the currently selected screen data regardless of what the Z80A microprocessor is doing. That includes if the Z80A is halted or it’s clock stopped.

All other video improvements that implemented by software are not normally described as video modes, because they require a lot of microprocessor time.

Although, the authors, creators, and software companies may market or describe them as a new ‘mode’.

Mark

“There are four lights!”

Step up to red alert. Sir, are you absolutely sure? It does mean changing the bulb

Looking forward to summer later in the year.

Re: Kernel start procedure

I find that it's generally people who don't understand what the software is doing that refer to video effects as a new screen 'mode'.

Re: Kernel start procedure

Probably new modes are possible. I saw few different screen definition as ZX Spectrum.

As we know from modern PC computers there are video systems assembled from hardware and software driver, program which could work as software interface or converter from anything we want to special hardware.

In this case as main key we should to choose one enumeric machine: 128k.

It has double buffering system.

Port $7FFD =SYSTEM VARIABLE:$5B5C

Bit Effect

7-6 Extra two bits for 16K RAM bank if in Pentagon 512K/1024K mode (see Next Memory

Bank Select $DFFD below)

5 1 locks pages; cannot be unlocked until next reset on regular ZX128)

4 128K: ROM select (0 = 128K editor, 1 = 48K BASIC)

+2/+3: low bit of ROM select (see +3 Memory Paging Control $1FFD above)

3 ULA layer shadow screen toggle (0 = bank 5, 1 = bank 7)

2-0 Bank number for slot 4 ($C000)

Bit #3 for shadow screen toggle 1 = bank 7 selected.

We can use it for double buffering at hardware level as described in manual. It is not the same as software dummy screen at own local position where ever we want.

Software procedure:

"The simplest way to implement double buffering on a 48K Spectrum is to set up a dummy screen

elsewhere in RAM, and draw all our background graphics and sprites there" ["How to write Spectrum Games" J.Cauldwell]]

But 128k can use hardware with banks 5 and 7. [sometimes I have read as "pages"].

"ULA always reads content from 16K bank 5. This is mapped to 16K slot 1 by default, addresses

$4000-$7FFF. ULA will always use bank 5, regardless of which bank is mapped to slot 1, or

which slot bank 5 is mapped to (or if it is mapped into any slot at all).

You can redirect ULA to read from 16K bank 7 instead (the “shadow screen”, used for doublebuffering), using bit 3 of Memory Paging Control $7FFD (page 41). However, you still need to

map bank 7 into one of the slots if you want to read or write to it (that’s 8K banks 14 and 15 if

using MMU for paging). Read more in ULA chapter, section 3.5, page 67." ["ZX Spectrum NEXT Assembly Developer Guide"].

Probably it would give to us 16kb+16kb=32 KB total per 1 frame

With video compression of CGA mode 4 bits per pixel +4 bits per pixel [111x111x] we could use all 50k pixels with color RGB x1.

In this case for sure these are TWO areas of HARDWARE video buffers where shold be placed data for display.

Now we should consider if double buffering for these two areas is for one full frame or 1/2 frame. And when video data are converted for pure ROWBLIT as true data of videos DAC.

Anybody who well knows hardware driver for that system which seems to be similar to the old CGA mode 16 colors could try to define own graphic software mode. If it will be possible or not depend on how much RAM is used in the system. Could help to us ZX512 or ZX4MB [max!].

ZX512 archive at EAGLE/link broken

ZX4MB archive

As we know from modern PC computers there are video systems assembled from hardware and software driver, program which could work as software interface or converter from anything we want to special hardware.

In this case as main key we should to choose one enumeric machine: 128k.

It has double buffering system.

Port $7FFD =SYSTEM VARIABLE:$5B5C

Bit Effect

7-6 Extra two bits for 16K RAM bank if in Pentagon 512K/1024K mode (see Next Memory

Bank Select $DFFD below)

5 1 locks pages; cannot be unlocked until next reset on regular ZX128)

4 128K: ROM select (0 = 128K editor, 1 = 48K BASIC)

+2/+3: low bit of ROM select (see +3 Memory Paging Control $1FFD above)

3 ULA layer shadow screen toggle (0 = bank 5, 1 = bank 7)

2-0 Bank number for slot 4 ($C000)

Bit #3 for shadow screen toggle 1 = bank 7 selected.

We can use it for double buffering at hardware level as described in manual. It is not the same as software dummy screen at own local position where ever we want.

Software procedure:

"The simplest way to implement double buffering on a 48K Spectrum is to set up a dummy screen

elsewhere in RAM, and draw all our background graphics and sprites there" ["How to write Spectrum Games" J.Cauldwell]]

But 128k can use hardware with banks 5 and 7. [sometimes I have read as "pages"].

"ULA always reads content from 16K bank 5. This is mapped to 16K slot 1 by default, addresses

$4000-$7FFF. ULA will always use bank 5, regardless of which bank is mapped to slot 1, or

which slot bank 5 is mapped to (or if it is mapped into any slot at all).

You can redirect ULA to read from 16K bank 7 instead (the “shadow screen”, used for doublebuffering), using bit 3 of Memory Paging Control $7FFD (page 41). However, you still need to

map bank 7 into one of the slots if you want to read or write to it (that’s 8K banks 14 and 15 if

using MMU for paging). Read more in ULA chapter, section 3.5, page 67." ["ZX Spectrum NEXT Assembly Developer Guide"].

Probably it would give to us 16kb+16kb=32 KB total per 1 frame

With video compression of CGA mode 4 bits per pixel +4 bits per pixel [111x111x] we could use all 50k pixels with color RGB x1.

In this case for sure these are TWO areas of HARDWARE video buffers where shold be placed data for display.

Now we should consider if double buffering for these two areas is for one full frame or 1/2 frame. And when video data are converted for pure ROWBLIT as true data of videos DAC.

Anybody who well knows hardware driver for that system which seems to be similar to the old CGA mode 16 colors could try to define own graphic software mode. If it will be possible or not depend on how much RAM is used in the system. Could help to us ZX512 or ZX4MB [max!].

ZX512 archive at EAGLE/link broken

ZX4MB archive

Last edited by TymoDEV on Sat Dec 03, 2022 5:20 pm, edited 1 time in total.

Re: Kernel start procedure

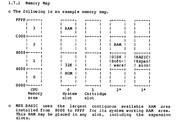

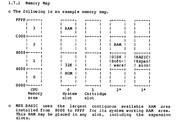

I have wrote this project of memory mapper:

<<<BANKS>>>

0....1....2.....3__________ A15,A16 ... lines from address bus

- - - - -- - - -

0....1....2...3

4....5....6...7

8 ...9...10..11

12..13..14..15______PAGES 0-31 [256 max]

16..17..18..19

20..21..22..23

24..25..26..27

28..29..30..31

|__|___|__|

128 |. 128 ..|

.....128 ... 128 kb each bank

Registers are:

$7FFD, $DFFD

Bit Effect of $DFFD

7 1 to set Pentagon 512K/1024K mode

3-0 Most significant bits of the 16K RAM bank selected in Memory Paging Control $7FFD

Next Memory Bank Select

$DFFD bits 3-0

$7FFD bits 2-0

Mapper for now fitted up to 512 kb pages 0-31.

I am not sure is it good mapper becuase I can not download it for now from that page. Link is broken. Last service update 2005.

<<<BANKS>>>

0....1....2.....3__________ A15,A16 ... lines from address bus

- - - - -- - - -

0....1....2...3

4....5....6...7

8 ...9...10..11

12..13..14..15______PAGES 0-31 [256 max]

16..17..18..19

20..21..22..23

24..25..26..27

28..29..30..31

|__|___|__|

128 |. 128 ..|

.....128 ... 128 kb each bank

Registers are:

$7FFD, $DFFD

Bit Effect of $DFFD

7 1 to set Pentagon 512K/1024K mode

3-0 Most significant bits of the 16K RAM bank selected in Memory Paging Control $7FFD

Next Memory Bank Select

$DFFD bits 3-0

$7FFD bits 2-0

Mapper for now fitted up to 512 kb pages 0-31.

I am not sure is it good mapper becuase I can not download it for now from that page. Link is broken. Last service update 2005.

Re: Kernel start procedure

If somebody can download these archives in .ZIP from https://8bit.yarek.pl (for EAGLE schematic)?

ZX512 download

ZX4MB download

ZX512 download

ZX4MB download

Re: Kernel start procedure

No. You get 7K per screen because the ULA only use 6912 bytes out of the 16K page. And you can't "use CGA mode" because the ULA doesn't do that. It decodes the video RAM in a very, very specific way and it's not something you can change - it is entirely fixed in hardware.TymoDEV wrote: ↑Sat Dec 03, 2022 4:12 pm

"ULA always reads content from 16K bank 5. This is mapped to 16K slot 1 by default, addresses

$4000-$7FFF. ULA will always use bank 5, regardless of which bank is mapped to slot 1, or

which slot bank 5 is mapped to (or if it is mapped into any slot at all).

You can redirect ULA to read from 16K bank 7 instead (the “shadow screen”, used for doublebuffering), using bit 3 of Memory Paging Control $7FFD (page 41). However, you still need to

map bank 7 into one of the slots if you want to read or write to it (that’s 8K banks 14 and 15 if

using MMU for paging). Read more in ULA chapter, section 3.5, page 67." ["ZX Spectrum NEXT Assembly Developer Guide"].

Probably it would give to us 16kb+16kb=32 KB total per 1 frame

With video compression of CGA mode 4 bits per pixel +4 bits per pixel [111x111x] we could use all 50k pixels with color RGB x1.

Re: Kernel start procedure

These options (16c) are for Russian machines only, not the original Spectrum. There are various ATM threads here, and @Alone Coder and others are experts on these machines.